#### Chapter 1: Fundamentals of Computer Design (Part 2)

What is computer architecture?

Why study computer architecture?

#### Common principles

Performance

What is performance: latency, throughput

The performance equation

Measuring performance

Improving performance: parallelism, locality, Amdahl's law

Power

Cost

Reliability

#### What is Performance?

Two Metrics

Latency (or response time or execution time)

Throughput (or bandwidth)

# Performance (Cont.)

Definition: X is n% faster than Y if

$\frac{Execution \ Time_Y}{Execution \ Time_X} = 1 + \frac{n}{100}$

Example: X = 1 minute, Y = 2 minutes

X is 100% faster than Y

# Key Performance Equation

$$CPU_{time} = \frac{instructions}{program} \ X \ \frac{cycles}{instruction} \ X \ \frac{time}{cycle}$$

Instructions per program (path length)

ISA and compiler

Cycles per instruction (CPI)

ISA and organization (e.g., cache misses)

Time per cycle (clock time, cycle time)

Organization and hardware

Sarita Adve

### **Measuring Performance**

MIPS, MFLOPS don't mean much

Benchmarks

Real programs

Representative of real workload

Only way to characterize performance

$\mathsf{SPEC89} \to \mathsf{SPEC92} \to \mathsf{SPEC95} \to \mathsf{SPEC} \ \mathsf{CPU2000} \to \mathsf{CPU2006} \to$

CPU2017

SPECFS, SPECWeb, SPECjbb, SPECvirt\_Sc2010, TPC

``Representative" program fragments

Often not representative of full applications

EEMBC for embedded systems

Toy benchmarks and synthetic benchmarks

Don't mean much

### Improving Performance – Basic Principles

Parallelism

Locality

Focus on common case - Amdahl's law

# Amdahl's Law

(Or why the common case matters most)

Let

$$Speedup = \frac{new\ rate}{old\ rate} = \frac{old\ latency}{new\ latency}$$

Consider an enhancement x that speeds up fraction  $f_x$  of a task by  $S_x$

$$\begin{aligned} Speedup_{overall} &= \frac{old\ latency}{new\ latency} \\ &= \frac{\{(1-f_x)+(f_x)\} \times old\ latency}{(1-f_x) \times old\ latency+f_x/S_x \times old\ latency} \end{aligned}$$

Amdahl's law gives

$$Speedup_{overall} = \frac{1}{(1 - f_x) + f_x / S_x}$$

### Amdahl's Law, cont.

Example:

$$f_x$$

= 95% and  $S_x$  = 1.10

$$Speedup_{overall} = \frac{1}{(1 - 0.95) + (0.95/1.10)} = 1.094$$

Example:  $f_x$  = 5% and  $S_x$  = 10

Speedup<sub>overall</sub> =

$$\frac{1}{(1 - 0.05) + (0.05/10)} = 1.047$$

Example:  $f_x$  = 5% and  $S_x$  =  $\infty$

Speedup<sub>overall</sub> =

$$\frac{1}{(1 - 0.05) + (0.05/\infty)} = 1.052$$

# Amdahl's Law Corollary

Since  $S_x \to \infty$  implies

$Speedup_{overall} = \frac{1}{(1 - f_x) + (f_x / \infty)}$

For all real speedups:

$Speedup_{overall} < \frac{1}{1 - f_x}$

Example  $f_x$  1/(1- $f_x$ )

1% 1.01

2% 1.02

5% 1.05

10% 1.11

20% 1.25

50% 2.00

Or make the common case fast

An application?

#### Power

Power

Energy

Temperature

# **Power and Energy**

Power = Dynamic power + Static power

Energy = Power \* Time

Dynamic Power ∞ Capacitance \* Voltage² \* Frequency

Static power = Static current \* Voltage

#### Cost

Cost is very important in most real designs

But usually hard to quantify for the architect

Costs change over time

Learning curve lowers manufacturing costs

Technology improvements lower costs

Focus on IC costs next

Sarita Adve 4

# **Integrated Circuit Cost**

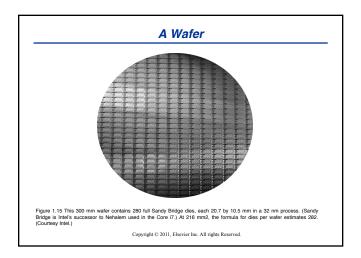

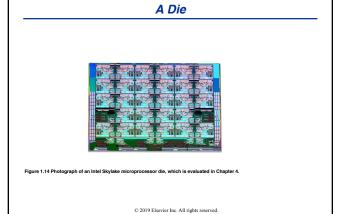

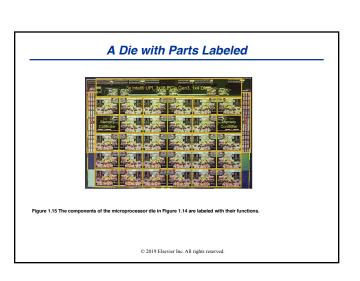

$$Cost \ of \ IC = \frac{Cost \ of \ Die + \ Cost \ of \ Testing + Cost \ of \ Packaging}{Final \ Test \ Yield}$$

$$Cost \ of \ Die = \frac{Cost \ of \ Wafer}{Dies \ per \ Wafer \times Die \ Yield}$$

Dies per Wafer =

$$(\frac{\pi \times (Wafer\ Diameter/2)^2}{Die\ Area})$$

–  $(Correction\ factor\ for\ Edge\ Effects)$

Die Yield = Wafer Yield

$$\times \frac{1}{(I + Defects\ per\ unit\ area \times Die\ Area)^{\alpha}}$$

$\alpha$ = 10 to 14 for 16nm in 2017

Bottom line: Cost per die grows roughly as the square of the die area Cost different from price; cost of manufacturing different from cost of operation

# Reliability

Many sources of unreliability

Soft errors due to radiation, hard errors due to wearout, ...

Common metrics

Mean time to failure – MTTF

For exponentially distributed time to failure

Define failures in time or FITs

FIT = failures in a billion hours

FIT α 1/MTTF

FIT of system = Sum of FITs of components

Common solution

Sarita Adve