## Chapter 3 – Instruction-Level Parallelism and its Exploitation (Part 5)

ILP vs. Parallel Computers Dynamic Scheduling (Section 3.4, 3.5) Dynamic Branch Prediction (Section 3.3, 3.9, and Appendix C) Hardware Speculation and Precise Interrupts (Section 3.6) Multiple Issue (Section 3.7) Static Techniques (Section 3.2, Appendix H) Limits and Benefits of ILP (Older editions and Section 3.12) Multithreading (Section 3.11) Putting it Together (Mini-projects)

## Limits of ILP

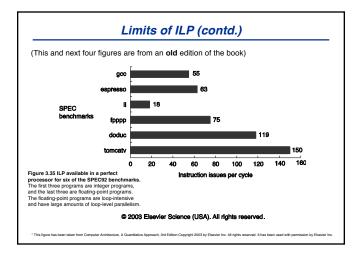

How much can ILP buy us?

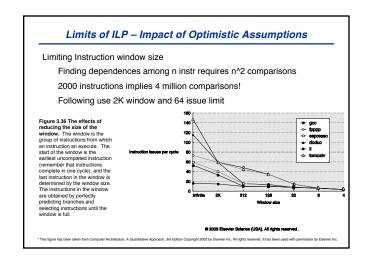

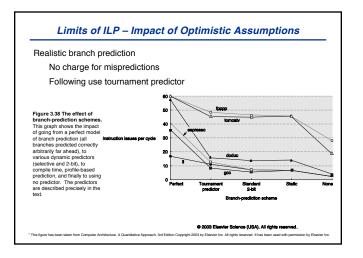

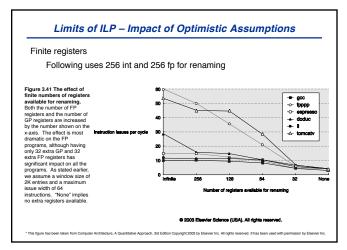

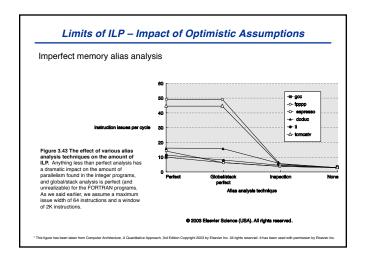

Limits studies make optimistic assumptions to find the limit for ILP But may miss impact of compiler, future advances A highly optimistic study [Wall'93] Infinite number of physical registers (no register WAW, WAR) Infinite number of in-flight instructions Perfect branch prediction Perfect memory address alias analysis Single cycle FU Single cycle memory (perfect caches)