| What is comp | uter architecture?                                   |

|--------------|------------------------------------------------------|

| Why study co | mputer architecture?                                 |

| Common prii  | nciples                                              |

| Performan    | ice                                                  |

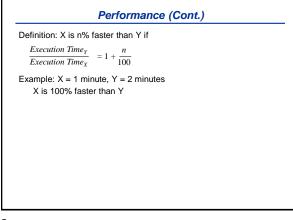

| What is      | s performance: latency, throughput                   |

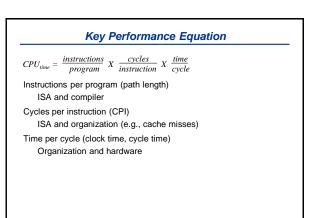

| The pe       | rformance equation                                   |

| Measu        | ring performance                                     |

| Improv       | ing performance: parallelism, locality, Amdahl's law |

| Power        |                                                      |

| Cost         |                                                      |

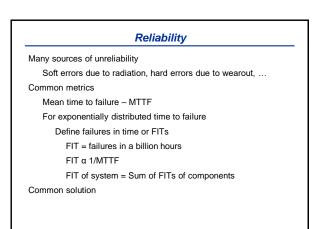

| Reliability  |                                                      |

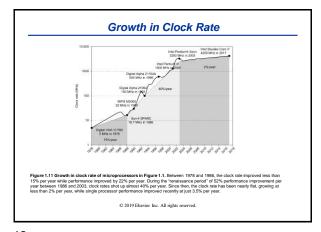

## Measuring Performance

MIPS, MFLOPS don't mean much Benchmarks Real programs Representative of real workload Only way to characterize performance SPEC89 → SPEC92 → SPEC95 → SPEC CPU2000 → CPU2006 → CPU2017 SPECFS, SPECWeb, SPECjbb, SPECvirt\_Sc2010, TPC Kernels ``Representative" program fragments Often not representative of full applications EEMBC for embedded systems Toy benchmarks and synthetic benchmarks Don't mean much

5

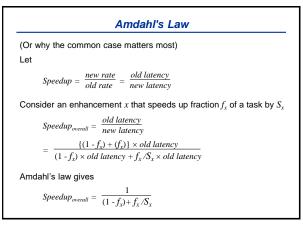

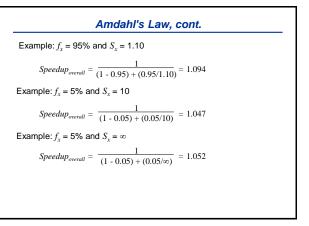

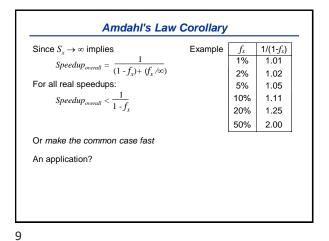

## Improving Performance – Basic Principles

Parallelism

Locality

Focus on common case - Amdahl's law

6

7

| Power       |  |  |

|-------------|--|--|

| Power       |  |  |

| Energy      |  |  |

| Temperature |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

10

Power and Energy Power = Dynamic power + Static power Energy = Power \* Time Dynamic Power ∞ Capacitance \* Voltage<sup>2</sup> \* Frequency Static power = Static current \* Voltage

11

Power and Energy

$Cost of IC = \frac{Cost of Die + Cost of Testing + Cost of Packaging}{Final Test Yield}$

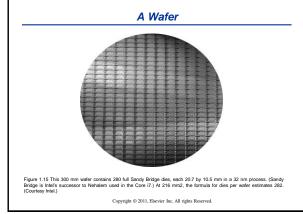

Cost of Die =  $\frac{Cost \ of \ Wafer}{Dies \ per \ Wafer \times Die \ Yield}$

Dies per Wafer =  $(\frac{\pi \times (Wafer \ Diameter/2)^2}{Die \ Area}) - (Correction \ factor \ for \ Edge \ Effects)$

Die Yield = Wafer Yield  $\times \frac{1}{(1 + Defects per unit area \times Die Area)^{\alpha}}$

$\alpha$ = 10 to 14 for 16nm in 2017

Bottom line: Cost per die grows roughly as the square of the die area Cost different from price; cost of manufacturing different from cost of operation